先进封装成破局,博通率先落地3.5D,6000mm²超大集成

电子发烧友网报道(文/莫婷婷)在全球 AI算力需求呈指数级爆发、传统摩尔定律逐渐失效的背景下,先进封装技术成为突破算力瓶颈的关键钥匙。就在近日, 博通(Bro adcom)宣布已开始向客户交付业界首款基于其3.5D超大尺寸系统级封装(X DSiP)平台打造的2纳米定制计算SoC。随着博通新品的交付,3.5D时代也加速到来。

重新定义维度:什么是3.5D XDSiP?

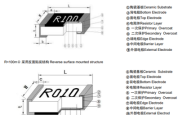

先进封装技术包括2.5D集成和3D集成等。

2.5D封装(如CoWoS)通过硅中介层将芯片并排连接,提升了带宽,实现了高速互连,但受限于中介层面积和布线长度, 信号延迟和功耗依然是挑战。

3D封装(如3D同质集成和3D异质集成)能通过微凸块或混合键合等方式实现多颗芯片的垂直堆叠,极大缩短互连距离,但在散热、良率及超大尺寸集成上面临巨大工艺难度。

图:盛合晶微SmartPoser®-3DIC-BP技术平台

尽管先进封装仍面临严峻的工艺挑战,但其带来的性能优势均不言而喻。正如盛合晶微在招股书中所述,以三维芯片集成(2.5D/3DIC)为代表的芯粒多芯片集成封装可以突破单芯片1倍光罩的尺寸限制,实现2倍、3倍光罩甚至更大尺寸范围内,数百亿甚至上千亿个 晶体管的异构集成。

正因如此,面对这些技术壁垒,以盛合晶微为代表的国内封装领军企业正持续加大研发投入,全力攻克关键难题。

而作为全球领先的 半导体解决方案供应商,博通提出3.5D XDSiP(eXtreme Dimension System in Package)技术,从架构上实现突破。

根据介绍,3.5D XDSiP技术是一款创新的多维堆叠芯片平台,结合了2.5D的大面积互联优势与3D-IC的垂直堆叠效率。区别于传统的3D堆叠多采用“背对面”(F ace-to-Back, F2B)或微凸块(Micro-bump)连接,其采用的是业界首创的面对面(Face-to-Face, F2F)3D混合铜键合技术,并且推出了推出业内首款面对面(F2F)3.5D XPU,使消费级AI客户能够开发下一代定制加速器(XPU)并计算 ASIC。

博通3.5D XDSiP主要有以下四大优势:一是增强互联密度,与F2B技术相比,叠加芯片间的信号密度提升了7倍。二是能源效率高,3.5D XDSiP采用3D HCB取代平面芯片对芯片PHY实现芯片对芯片接口的功耗10倍降低。三是延迟低,最小化3D堆栈中计算、内存和I/O组件之间的延迟。四是中介器和封装尺寸更小。

图:博通3.5D XDSiP技术平台

3.5D XDSiP平台实现了超大尺寸集成,在单一封装内集成超过6,000平方毫米的3D堆叠硅片,以及多达12个HBM(高带宽内存)堆栈。公开资料显示,在XPU开发中,当前采用2.5D封装的最先进AI芯片,其集成能力上限约为2,500平方毫米的硅面积和8颗HBM。这意味着,博通的新技术将芯片集成密度与内存带宽容量提升了逾一倍。

图:博通3.5D XDSiP技术平台

本文 zblog模板 原创,转载保留链接!网址:https://www.wbaas.cn/fengrong/1400.html

1.本站遵循行业规范,任何转载的稿件都会明确标注作者和来源;2.本站的原创文章,请转载时务必注明文章作者和来源,不尊重原创的行为我们将追究责任;3.作者投稿可能会经我们编辑修改或补充。